Latch

In elettronica digitale, il latch (lett. "serratura" o "chiavistello") è uno dei più importanti circuiti logici sequenziali asincroni. Costituisce una delle possibili implementazioni della cella di memoria elementare, ed è un elemento essenziale alla realizzazione di tutte le reti logiche sequenziali. E' importante non confondere il latch con il flip-flop: un circuito sincrono con la stessa funzione.[1]

Per definizione il latch rientra nella categoria dei multivibratori bistabili: è cioè un dispositivo caratterizzato da esattamente due stati stabili tra i quali può transire a comando. Questo lo rende adatto come cella di memoria, in quanto l'insieme delle configurazioni di output codifica esattamente 1 bit di informazione. [1] [2]

Diversamente dal flip-flop, il latch è un dispositivo sensibile al "livello" degli ingressi. In generale questo vuol dire che una transizione di stato viene innescata ogni qual volta la configurazione degli ingressi supera un certo stato soglia, che dipende dalla tecnologia usata per costruire il latch. Nella pratica questa caratteristica risulta spesso problematica ed è il principale fattore che rende i flip-flop un'alternativa preferibile.[3]

Oltre che come memoria il latch trova applicazione come dispositivo anti-rimbalzo nei circuiti che comprendono componenti elettromeccanici come pulsanti, interruttori e commutatori.

Latch SR

[modifica | modifica wikitesto]

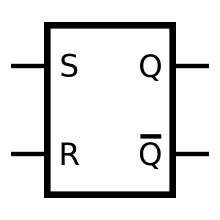

Il latch SR è il latch elementare, sul quale sono basati tutti gli altri. Si tratta di un semplice circuito a due ingressi e due uscite, composto da due porte logiche in retroazione mutua. Il nome deriva dalla denominazione dei due terminali di ingresso: S (per Set, lett. "imposta") ed R (per Reset, lett. "Reimposta").

A livello di logica booleana esistono due implementazioni del latch SR: la versione in logica congiuntiva negata (NAND) e quella in logica disgiuntiva negata (NOR). Le due versioni differiscono sostanzialmente solo nella semantica delle configurazioni di ingresso: nel primo caso si avrà un'interfaccia "attiva bassa" (logica negativa) mentre nell'altro sarà "attiva alta" (logica positiva).

A livello di implementazione elettronica digitale invece il discorso è più complesso e la versione NAND risulta in un circuito decisamente più efficiente.

Il comportamento del latch SR è relativamente semplice e può essere riassunto dal seguente sistema di espressioni:

Descrizione analitica del latch SR in logica congiuntiva. L'espressione in logica disgiuntiva può essere ricavata banalmente applicando i teoremi di De Morgan.

Principio di funzionamento

[modifica | modifica wikitesto]Nella versione attiva bassa, normalmente in modalità di immagazzinamento, gli input e vengono tenuti a livello logico alto così che il feedback mantenga gli output e in uno stato costante.

Quando viene abbassato il livello logico sull'input (set) l'output passa ad alto e resta alto anche quando torna alto. Al contrario, quando (reset) viene abbassato, l'output diventa basso e resta basso anche quando torna alto.

Se entrambi e assumono il valore 0, le uscite e assumono entrambe il valore 1, per definizione di NAND con una variabile di valore 0 (0 AND X risulta 0 e negato diventa 1). Il fatto che le uscite assumano lo stesso valore contraddice i nomi assegnati alle uscite (per i quali una dovrebbe essere la negata dell'altra), per questo viene chiamato stato non ammesso o non permesso, ma il circuito è stabile e mantiene entrambe le uscite alte. Il fenomeno di instabilità si verifica quando gli ingressi e passano simultaneamente dai valori 00 (non permesso) ai valori 11 (memoria). Nel caso di circuito ideale, quindi con tempi di propagazione dei segnali identici per le due porte logiche, si verifica il fenomeno di corsa critica e le uscite oscillano. Nei circuiti reali, per tempi di propagazione delle due porte molto simili, si può verificare uno stato metastabile con transizione finale casuale verso lo stato 10 o 01. Nei circuiti reali, con tempi di propagazione nelle due porte ragionevolmente diversi, si verifica uno stato intermedio di Set o Reset a seconda dei tempi e di conseguenza lo stato di memoria.

In maniera duale, nella versione attiva alta, lo stato di memoria si ottiene quando entrambi gli ingressi sono bassi. La funzione di reset avviene quando è alto l'ingresso R e la funzione set quando è alto l'ingresso S. La condizione da evitare perché lo stato dell'uscita resti indeterminato è quella dei due ingressi entrambi alti.

Nella tabella della verità del Latch SR le uscite e vengono a volte indicate come e per distinguerle dagli ingressi. Per esempio, per il latch attivo basso si ha:

| S̅ | R̅ | Q' | Q̅' | Funzione |

|---|---|---|---|---|

| 0 | 0 | x | x | Non è ammesso |

| 0 | 1 | 1 | 0 | Set |

| 1 | 0 | 0 | 1 | Reset |

| 1 | 1 | Q | Q̅ | Latch (Memorizzazione) |

mentre per il latch attivo alto:

| S | R | Q' | Q̅' | Funzione |

|---|---|---|---|---|

| 0 | 0 | Q | Q̅ | Latch (Memorizzazione) |

| 0 | 1 | 0 | 1 | Reset |

| 1 | 0 | 1 | 0 | Set |

| 1 | 1 | x | x | Non è ammesso |

Latch SR con abilitazione

[modifica | modifica wikitesto]

Il Latch SR con enable è una versione del latch SR che include un ulteriore ingresso, chiamato "enable" (E). Questo ingresso consente di controllare quando il latch può essere abilitato per l'aggiornamento del suo stato. Quando l'ingresso di enable è attivo (ad esempio, portato a 1), il latch risponde ai segnali sugli ingressi S e R come descritto per il latch SR standard. Tuttavia, quando l'ingresso di enable è disattivato (ad esempio, portato a 0), il latch mantiene il suo stato attuale, indipendentemente dai segnali sugli ingressi S e R.

Latch D

[modifica | modifica wikitesto]

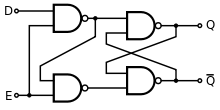

Il latch D (Data o Delay, lett. "Dato" o "Ritardo") è un circuito a due ingressi e due uscite, realizzato anteponendo ad un latch SR un circuito di pilotaggio, che rende irrealizzabile la configurazione instabile tipica del latch SR ed aggiunge la funzione di abilitazione.

È caratterizzato da un ingresso D (Data) sul quale va presentato il segnale da memorizzare, ed un ingresso E (Enable) che abilita o disabilita l'acquisizione del segnale D, e quindi la variazione dello stato di uscita.

Il comportamento del latch D può essere riassunto dalla seguente espressione:

Latch JK

[modifica | modifica wikitesto]Latch con preset e clear

[modifica | modifica wikitesto]Note

[modifica | modifica wikitesto]- ^ a b Mano, Kime, Martin 2019, pp. 184-186.

- ^ (EN) Claude Elwood Shannon, A mathematical theory of communication, in ACM SIGMOBILE Mobile Computing and Communications Review, vol. 5, n. 1, New York (NY, USA), Association for Computing Machinery, 1º gennaio 2001, p. 1, DOI:10.1145/584091.584093, ISSN 1559-1662.

- ^ Mano, Kime, Martin 2019, pp. 190-191.

Bibliografia

[modifica | modifica wikitesto]- Giuseppe Licata, Sistemi digitali. Per gli Ist. Tecnici, 1ª ed., Thecna, 29 giugno 2002, p. 512, ISBN 978-88-395-1377-9.

- M. Morris Mano, Charles R. Kime e Tom Martin, Reti logiche, a cura di Antonio Gentile, Filippo Sorbello e Salvatore Vitabile, traduzione di Silvia Franchini, et al., 5ª ed., Milano - Torino, Pearson, 2019, ISBN 978-88-919-0581-9.

Altri progetti

[modifica | modifica wikitesto] Wikizionario contiene il lemma di dizionario «Latch»

Wikizionario contiene il lemma di dizionario «Latch»

Collegamenti esterni

[modifica | modifica wikitesto]- latch, su Treccani.it – Enciclopedie on line, Istituto dell'Enciclopedia Italiana.

- latch, in Dizionario delle scienze fisiche, Istituto dell'Enciclopedia Italiana, 1996.

- latch, su Vocabolario Treccani, Istituto dell'Enciclopedia Italiana.

- (EN) Denis Howe, latch, in Free On-line Dictionary of Computing. Disponibile con licenza GFDL

| Controllo di autorità | GND (DE) 4219389-8 |

|---|