Architetture di sistemi multiprocessore

Un sistema informatico multiprocessore è un sistema che ha una struttura con più di un processore, ossia è composto da più unità di processo centrale (CPU) collegate tra loro [1].

Esistono varie architetture di sistemi multiprocessore, che sono classificabili in base alle seguenti caratteristiche:

- grado di accoppiamento: forte o debole;

- grado di diversificazione: omogeneo o eterogeneo;

- accesso alle risorse: uniforme, non uniforme, ibrido.

Sistema ad accompiamento debole[modifica | modifica wikitesto]

In un sistema multiprocessore, ciascun processore ha una sua memoria locale, i suoi canali di I/O (input-output) e un Sistema operativo indipendente. I processori possono scambiare dati attraverso una rete di connessione veloce tramite invio di messaggi (message passing).

Caratteristiche del sistema[modifica | modifica wikitesto]

- Questi sistemi sono in grado di eseguire istruzioni multiple su dati multipli (MIMD - Multiple Instruction Multiple Data);

- Questo tipo di architettura permette il calcolo parallelo (parallel processing).;La memoria distribuita permette un'elevata scalabilità.

Sistema ad accoppiamento forte[modifica | modifica wikitesto]

Sistema multiprocessore con memoria condivisa strettamente connessa ai processori.

Un sistema multiprocessore simmetrico è un sistema con una memoria centralizzata condivisa, chiamata memoria principale (Main Memory - MM), operante sotto il controllo di un singolo sistema operativo con uno o più sistemi multiprocessore.

Ci sono due tipi di sistemi:

- Sistema UMA;

- Sistema NUMA.

Sistema UMA[modifica | modifica wikitesto]

Sistema UMA (acronimo di Uniform Memory Access, lett. "accesso della memoria uniforme" in italiano)

- Sistema eterogeneo;

- Sistema multiprocessore simmetrico (SMP).

Sistema eterogeneo[modifica | modifica wikitesto]

Un sistema eterogeneo si riferisce ad un sistema che contiene unità di calcolo non omogenee (CPU - Central Processor Unit), processori grafici (GPU - Graphic Processor Unit), processori di segnali digitali, o ogni tipo di ASIC (application-specific integrated circuits). Questa tipo di architettura permette a qualsiasi processore dedicato, come un GPU, di operare allo stesso livello delle CPU.

Sistema simmetrico (SMP)[modifica | modifica wikitesto]

Sistema operante sotto un singolo sistema operativo con una memoria (MM) centralizzata condivisa.

Il Sistema multiprocessore simmetrico (SMP-Symmetric Multiprocessor System) è un sistema formato da un insieme di processori omogenei che lavorano indipendentemente. Ciascun processore, eseguendo programmi diversi su dati diversi, ha capacità di condividere risorse comuni (memoria, periferiche di I/O, sistema di interruzione ecc.) connessi tramite un Bus di sistema (system bus) o un crossbar (connessioni incrociate) o un mix dei questi due approcci, bus per gli indirizzi e crossbar per i dati (data crossbar)[2][3][4].

Ciascun processore ha una sua memoria cache che agisce come ponte tra i processori e la memoria principale (MM). La funzione della memoria cache è di velocizzare gli accessi dei dati della MM (aumento di prestazioni): nei sistemi multiprocessore a memoria condivisa è molto importante ridurre il traffico nel bus di sistema e di memoria, che è uno dei maggiori colli di bottiglia di questi sistemi. In questi sistemi la cache risulta perciò un elemento essenziale.

La condivisione della memoria garantisce un accesso uniforme alla MM (UMA - Uniform Memory Access time).

Sistema cc-NUMA[modifica | modifica wikitesto]

Sistema cc-NUMA (cache coherency - Non Uniform Memory Access, lett. "coerenza della cache - accesso alla memoria non uniforme" in italiano)

È noto che i sistemi SMP sono limitati in scalabilità (espansioni incrementali). Per superare questo limite, viene normalmente usata l'architettura chiamata "cc-NUMA".

Il sistema cc-NUMA è un gruppo di sistemi SMP chiamati "nodi" connessi a una rete di connessione veloce che può essere un link (collegamento) che può essere un anello singolo o un anello doppio bidirezionale oppure un multi-anello, connessione punto-punto[5][6] oppure infine un mix di questi (ad esempio IBM Power Systems[5][7]), bus (es. NUMAq[8]), crossbar, bus segmentato (segmented bus) (NUMA Bull HN ISI ex Honeywell[9]), Mesh router, ecc.

La caratteristica principale di questi sistemi è di avere un'unica memoria condivisa distribuita in ciascun nodo a cui possono accedere tutti i processori di tutti i nodi.

In un sistema cc-NUMA, l'accesso di un processore a una memoria remota di un nodo remoto è più lento rispetto ad un accesso alla sua memoria locale. Per questa ragione questo sistema è chiamato NUMA (Non Uniform Memory Access - accesso alla memoria non uniforme).

Il sistema cc-NUMA è anche chiamato Distributed Shared Memory (DSM) - memoria condivisa distribuita.[10]

Ciascun nodo normalmente è un sistema SMP, dove un processore può essere un singolo processore o un processore multi-core o un mix dei due o qualsiasi altro tipo di architettura.

La differenza di tempo di accesso tra locale e remoto può essere anche di un ordine di grandezza, dipendente dal tipo della rete di connessione usata (più veloce nel bus segmentato, crossbar o interconnessione punto-punto, più lenta nella connessione ad anelli seriali).

Esempi di interconnessione[modifica | modifica wikitesto]

Per superare questo limite normalmente viene usata usata una grande cache remota (vedi Cache remota). Con questa soluzione il sistema cc-NUMA diventa simile ad un esteso sistema SMP.

Gradi di accoppiamento a confronto[modifica | modifica wikitesto]

Entrambe le architetture hanno dei vantaggi e il compromesso tra i due può essere riassunto qui di seguito:

- Le architetture ad accoppiamento largo (loosely coupled) permettono alte prestazioni per ciascun singolo processore ma non sono in grado di ottenere in tempo reale un facile bilanciamento del carico tra processori.

- Le architetture ad accoppiamento stretto (tightly coupled) per contro sono in grado di fornire un facile bilanciamento ma soffrono di "colli di bottiglia" dovuti alla condivisione risorse comuni tramite uno o più bus (che sono anch'essi risorse comuni)[11].

Sistema con duplicazione dei dati globali[modifica | modifica wikitesto]

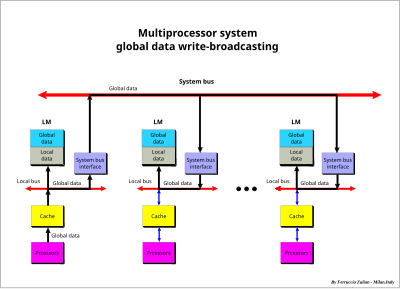

Questo sistema è un approccio intermedio fra le due architetture precedenti: ha sia risorse comuni a tutti i processori, che risorse e memoria locali (LM) in ogni processore. Le risorse comuni sono accessibili da tutti i processori tramite il bus di sistema, mentre le risorse locali sono accessibili solo al relativo processore locale. Le memorie cache, in questa prospettiva sono viste come memorie locali.

Questo sistema (patented F. Zulian[12]) usato nei sistemi Unix DPX/2 300 (Bull Hn Information Systems Italia (ex Honeywell))[13][14] è un mix tra sistemi tightly coupled e loosely coupled la cui caratteristica è quella di offrire tutti i vantaggi di queste due architetture.

La memoria locale è divisa in due sezioni, dati globali (Global Data - GD) e dati locali (Local Data - LD).

Il concetto base di questa architettura è di avere dati globali, che sono informazioni modificabili da tutti, che possono essere accedute da tutti i processori localmente, essendo queste informazioni duplicate in ciascuna memoria locale di ciascun processore.

Ogni volta che questi dati sono modificati in una memoria locale, un'operazione di scrittura globale viene inviata sul bus di sistema a tutte le altre memorie locali (write-broadcasting) per mantenere la coerenza dei dati globali. Perciò i dati globali possono essere letti localmente da ciascun processore senza dover accedere al bus di sistema. Il bus di sistema è acceduto solo quando i dati globali di una memoria locale sono modificati, per aggiornare la copia di questi dati memorizzati nelle altre memorie locali.

I dati locali invece possono essere scambiati in modo simile al sistema loosely coupled via message passing (invio di messaggi).

Note[modifica | modifica wikitesto]

- ^ http://www.cs.vu.nl/~ast/books/mos2/sample-8.pdf

- ^ Multi-processor system with shared memory - http://www.freepatentsonline.com/5701413.html

- ^ Method for transferring data in a multiprocessor computer system with crossbar interconnecting unit - https://www.google.it/patents/EP0923032A1?cl=en

- ^ Specification and Verification of the PowerScale Bus Arbitration Protocol: An Industrial Experiment with LOTOS, Chap. 2, Pag. 4 – ftp://ftp.inrialpes.fr/pub/vasy/publications/cadp/Chehaibar-Garavel-et-al-96.pdf

- ^ a b AMD Opteron Shared Memory MP Systems – http://www.cse.wustl.edu/~roger/569M.s09/28_AMD_Hammer_MP_HC_v8.pdf

- ^ An Introduction to the Intel® QuickPath Interconnect – http://www.intel.ie/content/dam/doc/white-paper/quick-path-interconnect-introduction-paper.pdf

- ^ IBM POWER Systems Overview, su computing.llnl.gov. URL consultato il 1º settembre 2018 (archiviato dall'url originale il 27 maggio 2010).

- ^ SourceForge – http://lse.sourceforge.net/numa/faq/system_descriptions.html

- ^ Bull HN F. Zulian – A. Zulian patent – Computer system with a bus having a segmented structure – http://www.freepatentsonline.com/6314484.html

- ^ NUMA Architecture – http://www.dba-oracle.com/real_application_clusters_rac_grid/numa.html

- ^ https://techdifferences.com/difference-between-loosely-coupled-and-tightly-coupled-multiprocessor-system.html

- ^ https://www.google.ch/patents/US4928224

- ^ http://www.feb-patrimoine.com/english/unix_and_bull.htm

- ^ http://www.feb-patrimoine.com/english/bull_dpx2.htm